**SPECIAL SECTION**

SCRUTINIZING LED LIGHTING Pg 51

EDN.comment Pg 6

Baker's Best Pg 20

Prying Eyes Pg 22

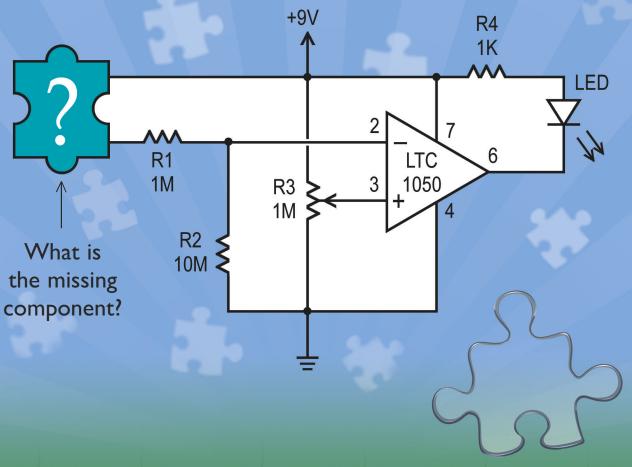

**Design Ideas** Pg 73

Seeing red over dead LEDs Pg 84

450,000+ PRODUCTS IN STOCK.

440+ SUPPLIER PARTNERS.

45,000+ NEW PRODUCTS ADDED IN THE LAST 90 DAYS.

The industry's broadest product selection available for immediate delivery

**www.digikey.com** 1.800.344.4539

Digi-Key is an authorized distributor for all supplier partners. New products added daily. © 2010 Digi-Key Corporation, 701 Brooks Ave. South, Thief River Falls, MN 56701, USA

# Show your team how it's done

Jump ahead with CST STUDIO SUITE™.

CST technology for SI/PI and EMC/EMI analysis.

→ Get equipped with leading edge 3D EM technology. CST's tools enable you to characterize, design and optimize electromagnetic devices all before going into the lab or measurement chamber. This can help save substantial costs especially for new or cutting edge products, reduce design risk and improve overall performance and profitability.

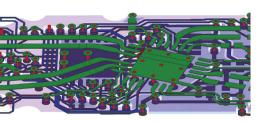

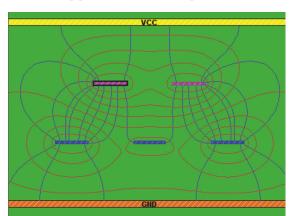

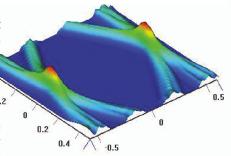

Involved in Signal or Power Integrity analysis? You can read about how CST technology was used to simulate and optimize an analog/digital multilayer PCB's performance at www.cst.com/pcb. If you're more interested in EMC/EMI or microwave components, we've a wide range of worked application examples live on our website at www.cst.com/apps

CST's flagship product, CST MICROWAVE STUDIO® [CST MWS], is the market leading time domain tool for 3D EM simulation. Embedded in an advanced design environment, CST MWS can be coupled with all CST STUDIO SUITE™ solver technology including PCB, circuit and thermal simulation.

ightarrow Grab the latest in simulation technology. Choose the accuracy and speed offered by CST STUDIO SUITE $^{\mathrm{IM}}$ .

CHANGING THE STANDARDS

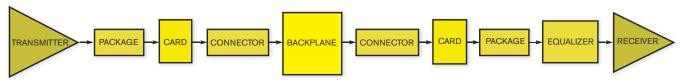

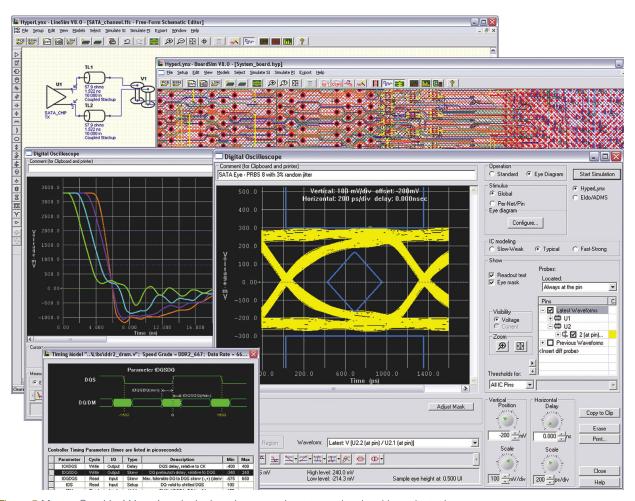

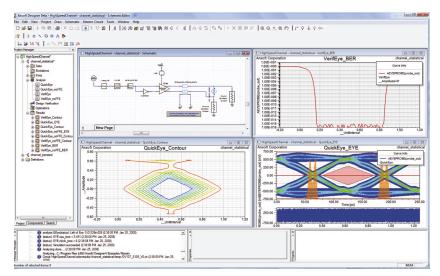

# Swimming in the channel

Signal-integrity problems can come back to bite you if you're not careful. Specialized software keeps the sharks away.

by Paul Rako, Technical Editor

# Polyphase filters reduce saturation

7 Polyphase techniques allow you to create large filters in smaller implementations in midrange FPGAs.

> by Ron Warner, Lattice Semiconductor Corp

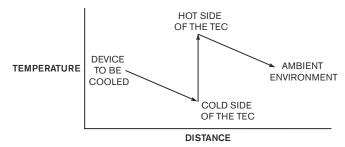

# Active heat removal cools electronics hot spots

1 A new approach to thermal management involves embedding functions deep inside an electronic component at the source of the heat using thermoelectric devices.

by Paul Magill, PhD, Nextreme Thermal Solutions Inc.

# Dilbert 12

- 11 Broadband VNA systems accurately characterize RF devices' nonlinear behavior

- 12 PLX delivers differentiation through evolution

- 12 Bar code enables traceability for individual LEDs

- 13 One-step graphene doping could enable graphene CMOS transistors

- 14 100-mm graphene wafers target next-generation electronics

- 14 SiGe mixer exhibits low noise. high linearity in wireless base stations

- 16 Smart power-meter-IC family offers alternative to current transformers

- 16 Calypto to power-management experts: Have it your way

- 18 Voices: Pierre-Yves Lesaicherre: Recognizing technology's inflections

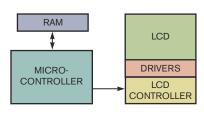

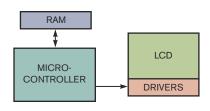

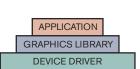

# Integrating midsized **LCDs**

7 When integrating LCDs into your design, you need to consider not only the cost of the LCD itself but also the costs of related hardware, software development, RTOS, and mechanical components. by Calvin Du.

MedX Health Corp

# ESIGNIDEAS

- 73 Strategy processes video in RAM

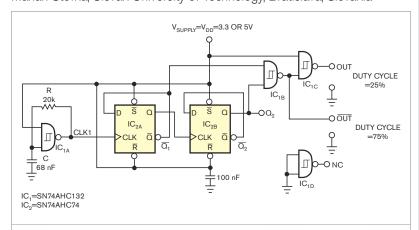

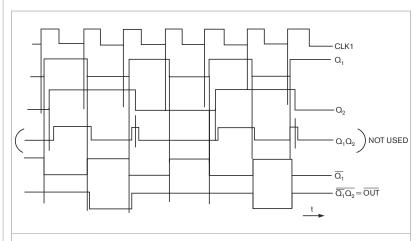

- 74 Rectangular-waveform generator produces 25 and 75% duty cycles

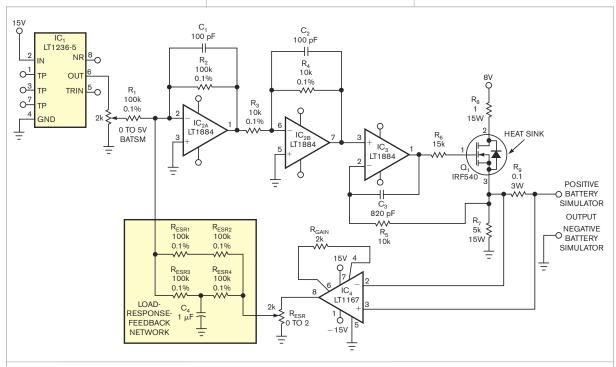

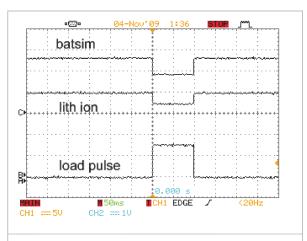

- 76 Battery simulator has variable ESR response

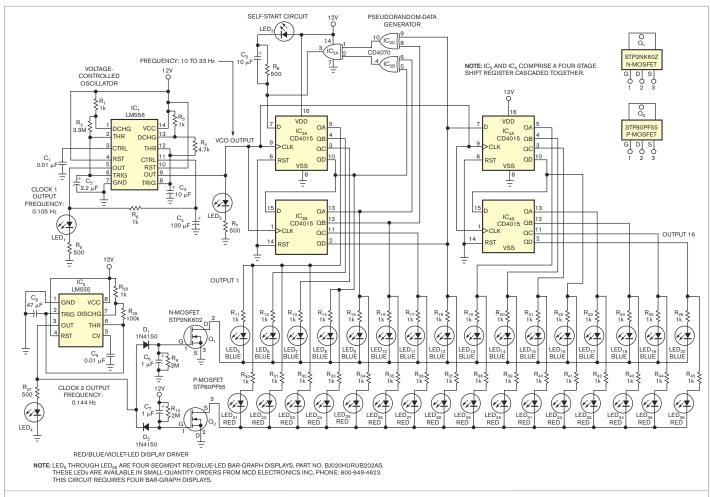

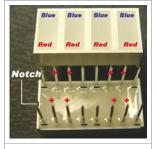

- 77 Create LED-lighting patterns without a controller

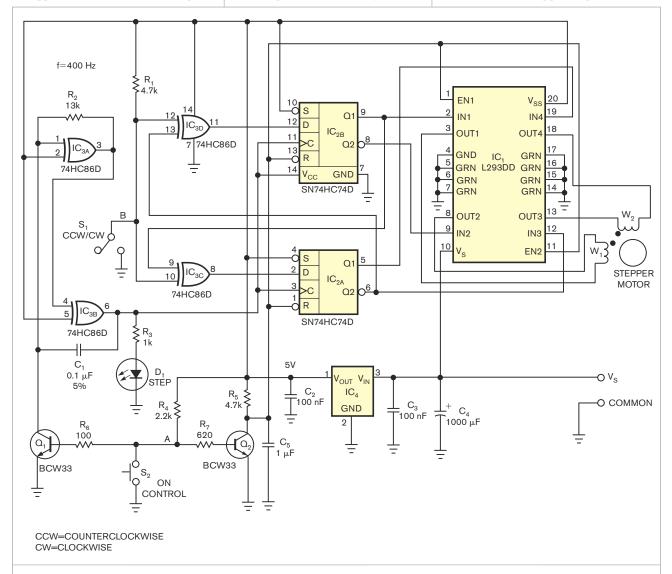

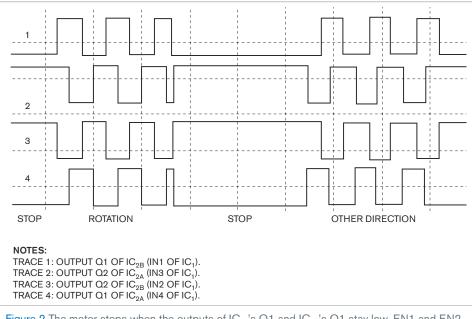

- 79 Control stepper motors in both directions

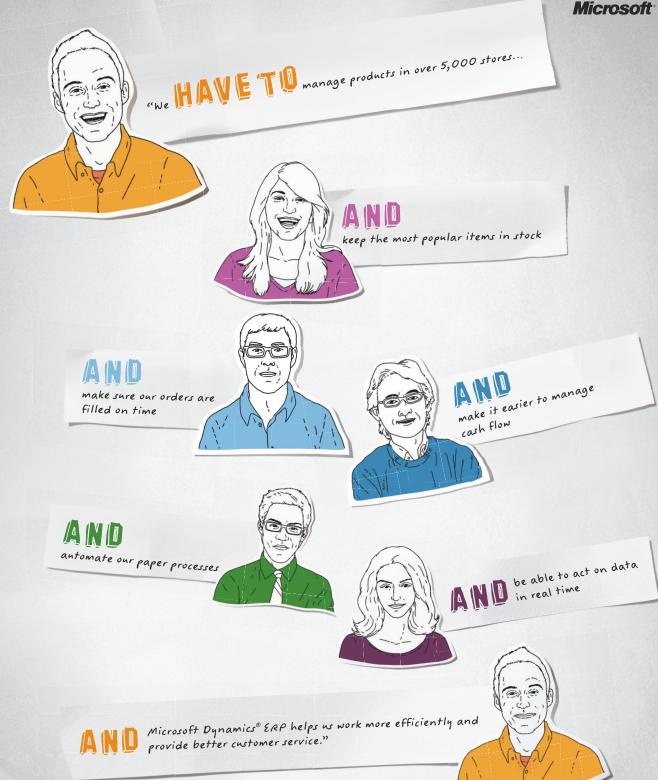

Microsoft Dynamics® ERP fits your company and business processes, not the other way around. It gives your people easier access to real-time actionable customer information for better decision-making and higher ROI.

To learn more about the efficiencies Microsoft Dynamics® ERP can create for your business, go to microsoftdynamics.com/manufacturing

# **The Newest Products** For Your Newest Designs

New Technologies are for Geniuses.

ASMT-Ax00 1W Power LED Light

mouser.com/avago1Wpowerled

Group SoL™ LED Lamps: R20/R30/R38 mouser.com/lightingsciencesolledlamps

WARNING: Designing with Hot, New Products May Cause A Time-to-Market Advantage.

You and your designs deserve the latest optoelectronic products and technologies. Experience Mouser's time-to-market advantage with no minimums and same-day shipping of the newest products from more than 400 leading suppliers.

mouser.com (800) 346-6873

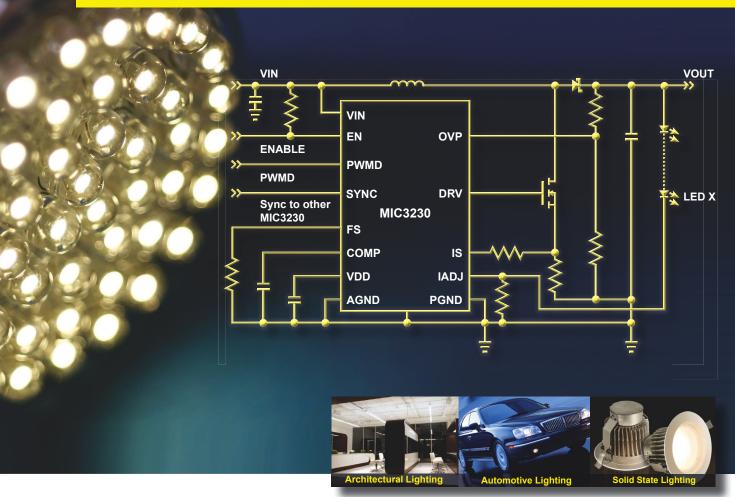

# SPECIAL SECTION Scrutinizing LED lighting

51 The LED-technology sector continues to be a growing industry. But its complex design requires integration of several potentially problematic components.

by Margery Conner, Technical Editor

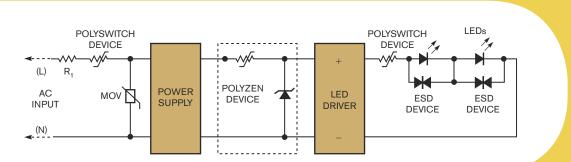

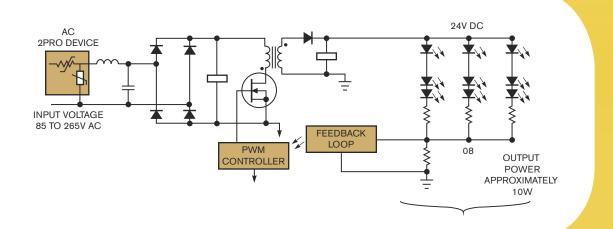

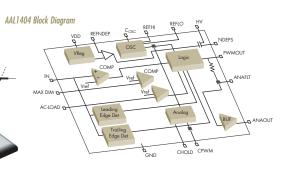

# 55 Circuit-protection strategies for improving LED reliability and lifetime

by Faraz Hasan, Tyco Electronics' Circuit Protection Business Unit

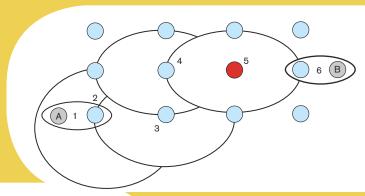

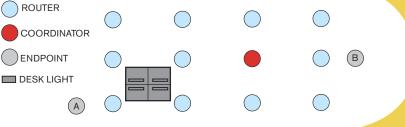

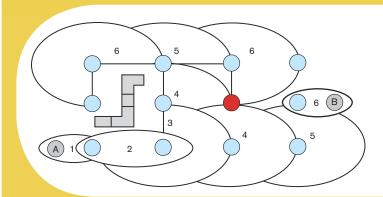

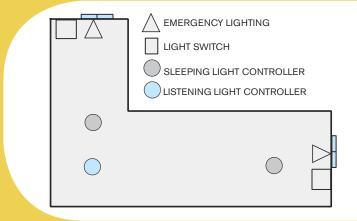

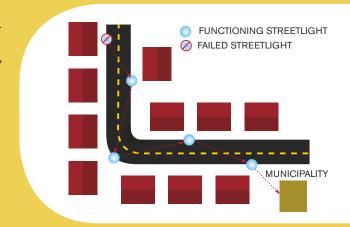

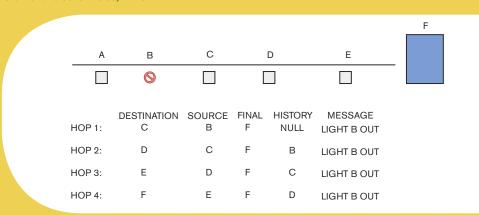

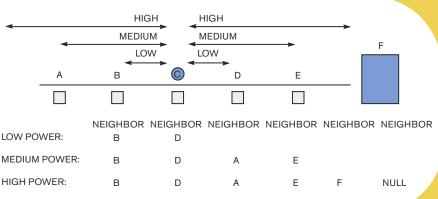

63 RF control for LEDlighting systems requires a variety of network types

> by Mike Claassen, Texas Instruments

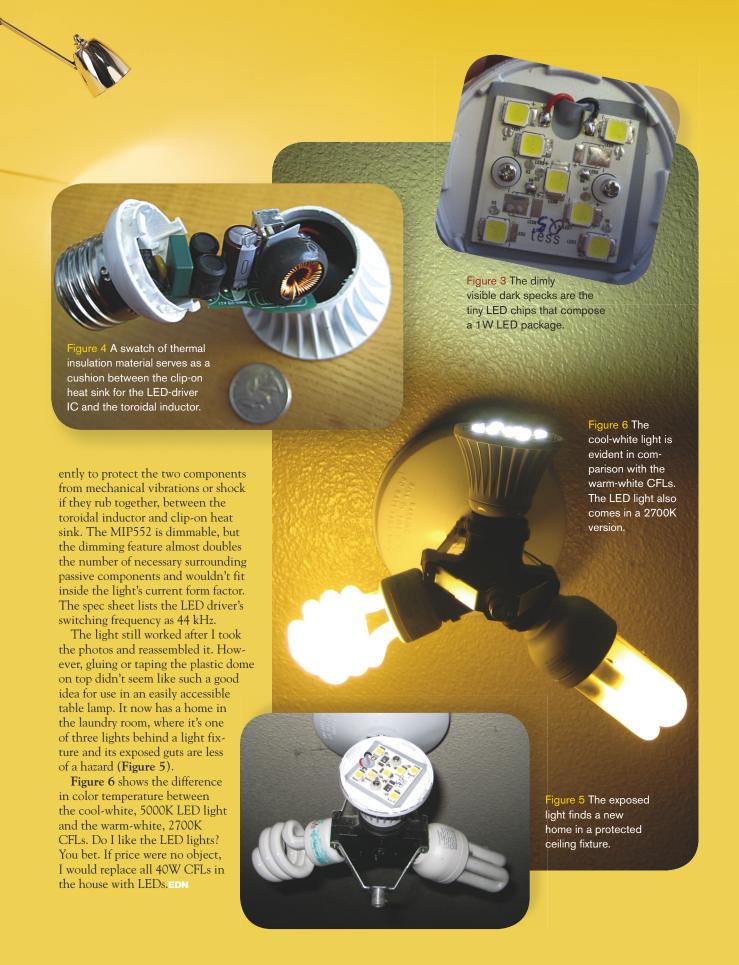

69 Tear-down: inside a 7W LED light bulb

by Margery Conner, Technical Editor

# **DEPARTMENTS & COLUMNS**

- **EDN.comment:** What happens after "I'm sorry": the world of product engineering

- 20 Baker's Best: System or technology dictates ADC choice

- 22 **Prying Eyes:** The Black and Decker GH1000 Type 2 string trimmer

- 24 Mechatronics in Design: Analogies give engineers insight

- 82 **Product Roundup:** Amplifiers, Oscillators, and Mixers

- 84 Tales from the Cube: Seeing red over dead LEDs

# **EDN** online contents

www.edn.com

# **ONLINE ONLY**

Check out this Web-exclusive article:

Combating congestion in highperformance, low-cost systems on chip

A few simple measures taken early in physical design can keep this killer from slaying

your tapeout schedule.

→www.edn.com/article/CA6720137

# INNO ATION

We are set to tally the votes for *EDN*'s 20th annual Innovation Award winners. Want to be the first to hear who wins? Purchase your ticket now for the big reveal. We'll name the winners April 26 during a reception in San Jose, CA.

→ www.edn.com/ innovation

# FROM EDN's BLOGS

Microsoft puts a bullet in my laptop from Leibson's Law, by Steve Leibson I'm not a knowing pirate; in fact. I consider my-

self a victim. But Microsoft was able to reach into my PC and brand me a pirate nevertheless. My mistake. I pay the price.

→www.edn.com/100318toc1

Google's Nexus One: initial hands-on frustrations and fun from Brian's Brain, by Brian Dipert I swapped my friend's

SIM card out of her T-Mobile G1 and into the Nexus One, and since then we've both been evaluating the old-versus-new hardware and software.

→www.edn.com/100318toc2

EDNIN (ISSN#O112-7515) is published semimonthly, 24 times per year, by Canon Communications LLC, 11444 W Olympic Blvd, Los Angeles, CA 90064-1549; 310/445-4200; FAX 310/445-4299, Periodicals postage paid at Los Angeles, California, and at additional mailing offices. SUBSCRIPTIONS—Free to qualified subscribers as defined on the subscription card. Rates for nonqualified subscriptions, including all issues: US, \$179.99 one year, Canada, \$229.99 one year, air expedited, \$399.99 one year. Except for special issues where price changes are indicated, single copies are available for \$10 US and \$15 foreign. For tele-phone inquiries regarding subscriptions, call 763/746-2792. Email: EDN@kmpsgroup.com. CHANGE OF ADDRESS—Notices should be sent promptly to PO Box 47461, Plymouth, MN 55447. Please provide old mailing labels as well as new address. Allow two months for change. NOTICE—Every precaution is taken to ensure accuracy of content; however, the publishers cannot accept responsibility for the correctness of the information supplied or advertised or for any opinion expressed herein, POSTMASTER—Send address changes to EDN, PO Box 47461, Plymouth, MS 5447. Canada Post: Publications Mail Agreement 40885220. Return undeliverable Canadian addresses to RCS International, Box 697 STN A, Windsor, Ontario N9A 6N4. Printed in USA. Copyright 2010 by Canno Communications LLC. All rights reserved. Reproduction in whole or part without written permission is prohibited.

# BY RON WILSON, EXECUTIVE EDITOR

# What happens after "I'm sorry": the world of product engineering

enior chip designers generally have a good understanding of the whole design flow. Fewer, even among senior designers, can speak with confidence about the tasks that start when silicon appears—the silicon bring-up process. And fewer still can speak comfortably about what happens when the new chip fails to come up properly: the realm we used to call failure analysis. That lack of information needs to change, argue two executives of that world, Presto Engineering's chief executive officer, Michel Villemain, and vice president of engineering, Frank Sauk.

To begin with, the two would like to change the name from failure analysis to product engineering. The reasons are deeper than just marketing spin. Villemain explains that there has been a profound shift in recent years in what actually goes on at this stage in the life of an IC design.

"A few years ago, a failure-analysis lab would have a focused-ion-beam system and maybe two or three additional pieces of equipment," he relates. When your chip didn't work, you'd record its faulty behavior on the bringup bench, diagnose the problem, develop a proposed ECO (engineering

change order) in simulation, and then send a die to the failure-analysis lab. The turnaround would be about 24 hours, and you could spin a mask with confidence.

Since then, SOCs (sys-

# Product engineering needs a new relationship with design and with the EDA industry.

tems on chips) have gone from four metal layers to 18. Access through the top of the die is impossible. So analysis of the die begins with lapping the back until the silicon is so thin that it's transparent and then retesting to make sure that you haven't broken anything. Probing and measuring then require a battery of mad-scientist tools, such as IR (infrared) imagers, lasers, and optical probes. "We are dealing with not-well-understood proxies of the signals we would really like to measure," Villemain says. Further, SOCs are so dependent on software to place them in a particular mode or state that the chip often must connect to system stubs and run real software just to establish the diagnostic loops that will create patterns for the probing equipment.

The nature of the questions has

changed, as well, Villemain continues. In the 180-nm days, the questions tended to be straightforward: Where is this signal getting inverted? Why isn't the bus request reaching the output pin? Today, the questions may leave product engineers with a lot less to go on. Where is all that leakage current coming from? Why isn't anything coming out of this scan chain? And turnaround times have stretched from hours to weeks. These changes justify the name change.

The changing environment requires more than new words, however. Product engineering needs a new relationship with design and with the EDA industry, Villemain and Sauk insist. "Designers need a primer—something to tell them this is what happens after tapeout," says Villemain.

Sauk agrees. "Design engineers need to understand what is and isn't possible in the lab and plan for product engineering as part of the process, not as some worrisome last resort," he says. That would mean, for instance, understanding the access requirements of the backside probing tools, and being prepared to help product engineers navigate the design database. Even such steps as preparing the die for the correct tool before sending it to the lab can make a week's difference in turnaround, Villemain says. Further, design teams could adjust their physical-design styles to assist the new tools, just as today backend designers place spare gates and ease congestion near suspicious circuits just in case there's a metal-mask ECO.

Similarly, product engineering needs a closer relationship with the EDA industry. "The test industry has DFT [design for test]," Villemain says. "We need to push for the EDA companies to understand that they have a significant role in product engineering, as well."EDN

Contact me at ronald.wilson@reed business.com.

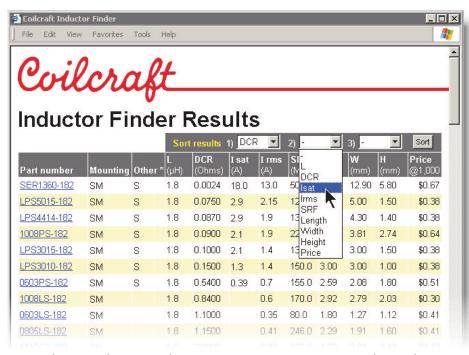

# Their sites have search engines. Ours has a <u>find</u> engine.

On most inductor web sites, their search engine results in more aggravation than answers.

But Coilcraft's web site is different.

In seconds, our Inductor Finder will show you all the parts that meet your electrical and size requirements. You can sort the results by your most important parameters. Compare pricing. Even analyze the core and winding losses of up to four different power inductors!

You'll find lots of other design tools to help you choose the perfect part. And then request free samples with just a few clicks.

So quit searching for magnetics and start finding them at www.coilcraft.com!

ISO9001-2000 ISO 14001 OHSMS 18001

Efficient Power for your applications

Http://www.mornsun-power.com

Tel: (+86)20-38601850 Fax: (+86)20-38601272 e-mail: info@mornsun.cn

DC-DC Converters • AC-DC Converters • Isolation Amplifier • LED Driver • IGBT Driver

#### PUBLISHER. EDN WORLDWIDE

Russell E Pratt, 1-781-734-8417; rpratt@reedbusiness.com

### ASSOCIATE PUBLISHER. **EDN WORLDWIDE**

Judy Hayes, 1-925-736-7617; judy.hayes@reedbusiness.com

#### **EDITOR-IN-CHIEF, EDN WORLDWIDE**

Rick Nelson, 1-781-734-8418; rnelson@reedbusiness.com

#### **EXECUTIVE EDITOR**

Ron Wilson, 1-510-744-1263; ronald.wilson@reedbusiness.com

#### MANAGING EDITOR Amy Norcross

1-781-734-8436; fax: 1-720-356-9161; amy.norcross@reedbusiness.com Contact for contributed technical articles

#### SENIOR ART DIRECTOR

Mike O'Leary 1-781-734-8307; fax: 1-303-265-3021; moleary@reedbusiness.com

#### **ANALOG**

Paul Rako, Technical Editor 1-408-745-1994; paul.rako@edn.com

#### MASS STORAGE, MULTIMEDIA, PCs, AND PERIPHERALS

Brian Dipert, Senior Technical Editor 1-916-760-0159; fax: 1-303-265-3187; bdipert@edn.com

#### MICROPROCESSORS, DSPs, **AND TOOLS**

Robert Crayotta Technical Editor 1-661-296-5096; fax: 1-303-265-3116: rcravotta@edn.com

### **NEWS**

Suzanne Deffree, Managing Editor 1-631-266-3433; sdeffree@reedbusiness.com

#### POWER SOURCES. **ONLINE INITIATIVES**

Margery Conner, Technical Editor 1-805-461-8242; fax: 1-805-461-9640; mconner@reedbusiness.com

### **DESIGN IDEAS EDITOR**

Martin Rowe, Senior Technical Editor, Test & Measurement World edndesignideas@reedbusiness.com

#### SENIOR ASSOCIATE EDITOR

Frances T Granville 1-781-734-8439; fax: 1-303-265-3131: f.granville@reedbusiness.com

## **EDITORIAL/WEB PRODUCTION**

Diane Malone, Manager 1-781-734-8445; fax: 1-303-265-3024 Steve Mahoney Production/Editorial Coordinator

1-781-734-8442: fax: 1-303-265-3198 Melissa Annand,

Web Operations Specialist 1-781-734-8443: fax: 1-303-265-3279 Adam Odoardi, Prepress Manager 1-781-734-8325; fax: 1-303-265-3042

### CONSULTING EDITOR

Jim Williams, Staff Scientist, Linear Technology

### CONTRIBUTING TECHNICAL EDITORS

Dan Strassberg, strassbergedn@att.net Nicholas Cravotta, editor@nicholascravotta.com

#### **COLUMNISTS**

Howard Johnson, PhD, Signal Consulting Bonnie Baker, Texas Instruments Pallab Chatterjee, SiliconMap

#### **PRODUCTION**

Dorothy Buchholz, **Group Production Director** 1-781-734-8329 Joshua S Levin-Epstein, Production Manager 1-781-734-8333; fax: 1-781-734-8096

### **EDN EUROPE**

Graham Prophet, Editor, Reed Publishing +44 118 935 1650; gprophet@reedbusiness.com

### EDN ASIA

Luke Rattigan, Chief Executive Officer luke.rattigan@rbi-asia.com Kirtimaya Varma, Editor-in-Chief kirti.varma@rbi-asia.com

### EDN CHINA

William Zhang, Publisher and Editorial Director wmzhang@rbichina.com.cn Jeff Lu, Executive Editor jefflu@rbichina.com.cn

### EDN JAPAN

Katsuya Watanabe, Publisher k.watanabe@reedbusiness.jp Ken Amemoto, Editor-in-Chief amemoto@reedbusiness.jp

EDN. 225 Wyman St, Waltham, MA 02451. www.edn.com. Phone 1-781-734-8000. Subscription inquires: 1-763-746-2792; EDN@kmpsgroup.com. Address changes: Send notice promptly to PO Box 47461, Plymouth, MN 55447. Please provide an old mailing labels as well as your new address. Allow two months for the change. Canon Communications LLC, 11444 W. Olympic Blvd., Los Angeles, CA 90064-1549; 1-310-445-4200; fax: 1-310-445-4299

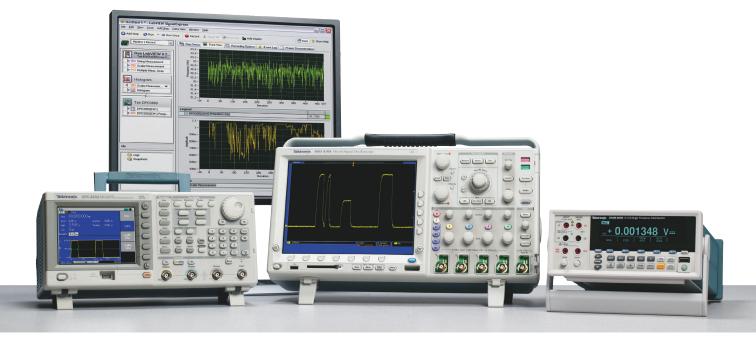

# Not Your Average Test Bench

Now it's easier than ever to debug those complex designs

Debug is hard enough. Don't let your test instruments get in the way. Our test bench offers the same ease-of-use you've come to expect from our oscilloscopes. From dedicated buttons for common functions to USB ports for saving data. To simplify your most complicated tasks, you can connect your test bench with the included copy of LabVIEW SignalExpress™ from National Instruments. Control your Tektronix instruments right from your PC. Automate measurements and analyze data across multiple instruments. Capture and save results. Create reports. Take your test bench from average to extraordinary.

## **Basic Oscilloscopes**

- 40 MHz to 500 MHz bandwidth

- Up to 25 automatic measurements

- Battery operation available\*

# Bench Oscilloscopes

- 100 MHz to 1 GHz bandwidth

- Up to 4 analog and 16 digital channels

- Parallel and serial bus analysis

- Power and video analysis

- Wave Inspector® for fast navigation of data

## Digital Multimeters NEW!

- 5.5 digit and 6.5 digit resolution

- Dual display

- Statistics, histogram and trending modes

# Arbitrary/Function Generators

- Up to 240 MHz bandwidth

- One or two channel models

- 12 standard waveforms, including arbitrary

Industry Leading 3-Year Warranty included with all Tektronix bench instruments.

www.tektronix.com/extraordinary

# MEET THE GUY that ELIMINATED HIS TEAM'S MANUFACTURING VARIABILITY ISSUES.

FIX YOUR MANUFACTURING VARIABILITY PROBLEMS AND YOUR REPUTATION WILL PRECEDE YOU. If you're designing chips for high functionality, high speed and lower power consumption at the most advanced process nodes, you've got variability issues. We have the solution that will increase your yield, performance and prestige by a wide margin. | Get more information at mentor.com/solutions/manufacturing-variability.

# Broadband VNA systems accurately characterize RF devices' nonlinear behavior

nritsu has introduced a nonlinearmeasurement system comprising its VectorStar broadband VNA (vectornetwork-analyzer) hardware and software that addresses the market demand for precise nonlinear vector analysis. The system enables engineers to accurately characterize the nonlinear behavior of RF devices, such as power amplifiers for emerging wireless-communication designs. The system offers a variety of configurations, provides fast measurements through real-time tuning, and performs accurate load-pull measurements, eliminating hours of load-pull-tuner calibration time. In addition, the system works with customer-owned tuners, permitting low-cost upgrades and allowing incremental configuration for true balanceddifferential active-device measurements.

The unit achieves the industry's best performance by integrating the VectorStar hardware with software that uses a new approach to acquiring the data necessary for nonlinear-device design and optimization. The software, which Anritsu developed with HFE SAGL (High-Frequency Engineering Società a Garanzia Limitata, www.hfemicro.com), provides nonlinear information in a variety of formats to facilitate RF-device analysis, design, and evaluation. By supporting the use of passive or active tuners or a combination of both, the hardware provides the most complete and accurate nonlinear load-pull data and offers the lowest-cost upgrade paths. The system inserts a low-loss coupler between the DUT (device under test) and the tuner to achieve accurate DUT source- and load-impedance measurements. The software provides immediate display of the DUT's performance based on changes in impedance, allowing for realtime tuning. This approach also eliminates the

need for precalibrated tuners and, by allowing monitoring of the DUT impedance during measurements, reduces the importance of tuner repeatability.

The unit can also provide a nonlinear DUT's measured parameters. You can use these parameters to design an optimum impedancematching network, or, for model simulation and development, you can export the parameters to an EDA program, such as Microwave Office (http://web.awrcorp.com/Usa/Products/ Microwave-Office). Anritsu officials believe that the choice of immediate design or model simulation is superior to the black-box-only approach of systems that require an EDA program. The US price starts at \$231,875 for the 20-GHz nonlinear system. Current VectorStar VNA users can easily upgrade to a nonlinear system by adding the software, test set, and components.-by Dan Strassberg

>Anritsu, www.anritsu.com.

FEEDBACK LOOP "Don't people realize how dangerous tampering with our brains is? ... Nobody touches my brain, and nobody decides where I look but me!"

—Controls engineer Bruce Koerner, in EDN's Feedback Loop, at www.edn.com/article/ CA6718485. Add your comments

Based on the manufacturer's VectorStar broadband VNA, this system measures nonlinear RF-device parameters with what the company terms unsurpassed accuracy.

# PLX delivers differentiation through evolution

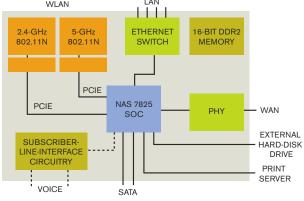

LX Technology recently announced its third generation of NAS (network-attached-storage) devices and the first it developed under the PLX umbrella (see "Integration amassed: analyzing a NAS," *EDN*, Jan 21, 2010, pg 16, www.edn.com/article/CA6715773).

The NAS 7820, 7821, and 7825 embed dual ARM 11 microprocessor cores running at 750 MHz, a companion network processor, and various application-specific hardware engines and software-acceleration modules. Single- and dual-port RGMII (reduced-gigabit-media-independent-interface) support enables integrated router and gateway functions, and two of the three family members embed

dual SATA (serial-advanced-technology-attachment) transceivers for RAID (redundant-array-of-inexpensive-disk) capabilities.

Other differentiators include two PCIe (Peripheral Component Interconnect Express) Version 1.0 ports on the highend 7825 and one each on the other two products, along with dual USB (Universal Serial Bus) 2.0 transceivers on all three devices. They all offer UART (universal-asynchronous-receiver/transmitter), SPI (serial-peripheral-interface). I<sup>2</sup>C (inter-integrated-circuit), and JTAG (Joint Test Action Group) capabilities, and the 7825 also has SPDIF (Sony/ Philips digital-interface-format) and TDM (time-division-multiplexed)/PCM (pulse-code-

PLX's processors

can directly

boot from the

system's disk

drives.

modulation)-interface features,

targeting applications such as

modulation)-interface features, targeting applications such as digital video recorders and settop boxes.

The devices' GbE (gigabit-Ethernet) MAC (media-access controller) includes a bandwidth-boosting TCP/IP (Transmission Control Protocol/Internet Protocol) offload engine. Integrated SRAM holds frequently used data, and onboard nonvolatile semiconductor storage is unnecessary because PLX's processors can directly boot from the system's disk drives. The devices and their companion development kits will enter general sampling this quarter; full production will follow in the second quarter. The NAS 7825 costs \$15 (volume quantities), and the 7821 and 7820 sell for \$13 and \$11, respectively. All three devices come in a 17×17-mm, 256bump FBGA package.

—by Brian Dipert ▶PLX Technology, www. plxtech.com.

The NAS 7825 device integrates two PCle ports and dual USB 2.0 transceivers.

# **DILBERT By Scott Adams**

# BAR CODE ENABLES TRACEABILITY FOR INDIVIDUAL LEDs

Some automotive and consumer-electronics customers require traceability down to the component level, and, for that reason, Philips Lumileds has implemented complete forward and backward traceability for its Luxeon power-LED product line. This feature allows the company to identify hundreds of

Bar codes allow full traceability for Luxeon power LEDs.

millions of LEDs' time, location, and technology of manufacture-down to the wafer level. The company claims that it is the first LED manufacturer to adopt this level of manufacturing control. Philips expects the solid-state lighting industry to require a similar degree of traceability.

by Margery ConnerPhilips Lumileds, www.philipslumileds.com.

# One-step graphene doping could enable graphene CMOS transistors

esearchers at the Georgia Institute of Technology have claimed a one-step process that produces both N- and P-type doping of large-area graphene surfaces and that could facilitate the use of the material for future electronic devices. The doping technique, which the researchers produced by applying a commercially available SOG (spin-on-glass) material to graphene and then exposing it to electron-beam radiation, can also increase conductivity in graphene nanoribbons for interconnects.

The team created both types of doping by varying the exposure time to the e-beam radiation; higher levels of e-beam energy produce P-type areas, and lower levels produce Ntype areas. The researchers used the technique to fabricate high-resolution PN junctions. When the team properly passivates the SOG, it creates doping that should remain indefinitely in the graphene sheets.

"This is a step toward making possible complementarymetal-oxide graphene transistors," says Raghunath Murali, a senior research engineer in Georgia Tech's Nanotechnology Research Center.

In the doping process, Murali and graduate student Kevin Brenner removed flakes of one- to four-layer-thick graphene from a block of graphite. Next, they placed the material onto a surface of oxidized silicon and fabricated a fourpoint contact device. They then spun on films of HSQ (hydrogen silsesquoxane) and cured certain portions of the resulting thin film using e-beam radiation. The technique provides precise control over the amount of radiation and where it is applied to the graphene; higher levels of energy correspond to more cross-linking of the HSQ.

"We gave varying doses of electron-beam radiation and then studied how it influenced the properties of carriers in the graphene lattice," says Murali. "The e-beam gave us a fine range of control that could be valuable for fabricating nanoscale devices. We can use an electron beam with a diameter

The process is the first to provide both electron (N-type) and hole (P-type) doping from a single dopant material.

of 4 or 5 nm that allows very precise doping patterns." Electronic measurements show that the technique creates a graphene PN junction with large energy separations, indicating strong doping effects.

Researchers elsewhere have demonstrated graphene doping using a variety of processes, including soaking the material in various solutions and exposing it to a variety of gases. Georgia Tech believes its process is the first to provide both electron (N-type) and hole (P-type) doping from a single dopant material. In the process, the doping introduces atoms of hydrogen and oxygen in the vicinity of the carbon lattice. The oxygen and hydrogen do not replace carbon atoms but instead occupy locations atop the lattice structure.

In volume manufacturing, a conventional lithography process would likely replace the e-beam radiation. Varying the reflectance or transmission of the mask set would control the amount of radiation reaching the SOG, and that variation would determine the creation of N- or P-type areas.

"Making everything in a single step would avoid some of the expensive lithography steps," says Murali. "Gray-scale

lithography would allow fine control of doping across the entire surface of the wafer."

For doping bulk areas, such as interconnects, that require no patterning, the researchers coat the area with HSQ and expose it to a plasma source. The technique can make the nanoribbons as much as 10 times more conductive than untreated graphene. However, the researchers note that they require a better understanding of how the process works and whether other polymers might provide better results. "We need to have a better understanding of how to control this process because variability is one of the issues that must be controlled to make manufacturing feasible," says Murali. "We are trying to identify other polymers that may provide better control or stronger doping levels."

The Semiconductor Research Corp (www.src.org) and the Defense Advanced Research Projects Agency (www. darpa.mil) through the Interconnect Focus Center (www. ifc.gatech.edu) supported the research, which a paper in Applied Physics Letters describes (Reference 1).

-by Suzanne Deffree Georgia Institute of Technology, www.gatech.edu.

# REFERENCE

Brenner, Kevin, and Raghunath Murali, "Single step, complementary doping of graphene," Applied Physics Letters, Feb 10, 2010, http://scitation.aip.org/ vsearch/servlet/VerityServlet ?KEY=APPLAB&smode= strresults&sort=chron&maxd isp=25&threshold=0&possi ble1=Raghunath+Murali&po ssible1zone=article&OUT LOG=NO&viewabs=APPL AB&key=DISPLAY&doc ID=1&page=1&chapter=0.

Georgia Tech graduate student Kevin Brenner holds a fabricated graphene sample (courtesy Georgia Institute of Technology).

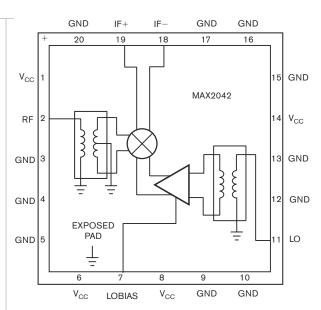

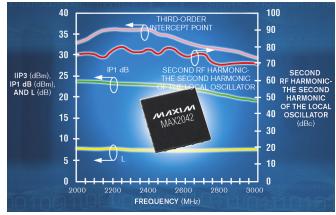

# SiGe mixer exhibits low noise, high linearity in wireless base stations

axim Integrated Products' new MAX2042 upconverting and downconverting, double-balanced passive mixer operates at 2 to 3 GHz. The SiGe (silicon-germanium) chip includes an internal local-oscillator buffer and two baluns. It outputs an intermediate frequency of 50 to 500 MHz. Power consumption is 690 mW at 5V and 396 mW at 3.3V. Typical applications include LTE (longterm evolution), wireless base stations, WiMax (worldwide interoperability for microwave access), MMDS (multipointmultichannel-distribution service), and WCS (wireless-communications service).

When operating as a downconverter from 5V, the part has a minimum IP3 (third-order intercept point) of 34 dBm (decibels relative to 1 mW). At 3.3V, the typical IP3 is 31 dB. The single-sideband noise figure is 7.3 or 7.5 typical when operating from 5 and 3.3V, respectively. The device's typical small-signal-conversion loss

is 7.2 dB at a 3.3 or 5V supply voltage. The second RF harmonic minus the second harmonic of the local oscillator spurs minimum rejection ranges of 54 dBc (decibels relative to the carrier) at 0-dBm output power and a 5V supply to typical rejection of 72 dBm at -10-dBm output power and a 3.3V supply.

When you operate the part as an upconverter, the MAX2042 delivers a minimum IIP3 of 30 dBm at 5V and 29.5 dBm typical at a 3.3V power-supply voltage. The typical smallsignal-conversion loss is 6.8 dB for a 3.3 or 5V supply voltage. The unit achieves 67 dBc suppression of the local oscillator plus or minus the second harmonic of the intermediate frequency.

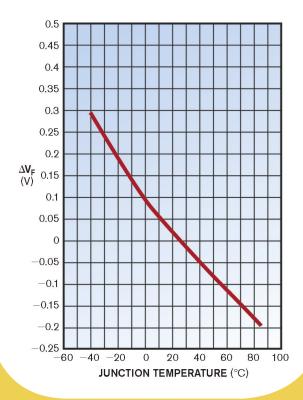

The MAX2042 operates at a -40 to +85°C junction temperature, comes in a 5×5-mm, 20-pin TQFN package, and sells for \$5.95 (1000).

-by Paul Rako **⊳Maxim Integrated Pro-**

ducts, www.maxim-ic.com.

The MAX2042 mixer uses a silicon-germanium process to provide good linearity and low noise.

The MAX2042 mixer has integrated baluns and a local-oscillator buffer.

# 100-mm GRAPHENE WAFERS TARGET NEXT-GENERATION ELECTRONICS

Researchers at the EOC (Electro-Optics Center) at Pennsylvania State University's Materials Research Institute have produced 100-mm-diameter graphene wafers. Using silicon sublimation, EOC researchers David Snyder and Randy Cavalero thermally processed silicon-carbide wafers in a physical-vapor-transport furnace until the silicon migrated away from the surface, leaving behind a layer of carbon that formed into a one- to two-atom-thick film of graphene on the wafer surface.

The researchers are initially focusing on graphene materials to improve transistor performance in various RF applications,

This 100-mm graphene wafer contains approximately 75,000 devices and test structures. The a single chip. Each small square pad on the chip measures 100 microns (courtesy Pennsylvania State University).

with Penn State developing graphene-device processing to enhance graphene-transistor performance. The university has also fabricated RF FETs on 100-mm graphene wafers. The researchers plan to improve the electron mobility of the silicon-sublimated wafers to nearer the theoretical limit, which is approximately 100 times faster than silicon.

The researchers are also using a nonsublimation approach to developing synthesis and device fabrication of graphene on silicon as a means to achieve wafer diameters exceeding 200 mm.-by Suzanne Deffree

**Pennsylvania State University Materials** Research Institute, www.mri.psu.edu.

# **Rarely Asked Questions**

Strange stories from the call logs of Analog Devices

# Taming A/D Converter Power Supplies

Q. Will a switching power supply (dc-to-dc converter) really degrade the A/D converter's performance?

**A.** Engineers commonly feel that a switching power supply can degrade the performance of an A/D converter, leading them to choose a low dropout (LDO) linear regulator over a switcher, but this perception isn't entirely true. LDOs have lower ripple and noise specifications, but recent studies show that efficient switchers can be employed in some converter designs provided the designer understands the topology, applies some practical know how, and takes the required precautions.

First choose the converter and then choose the right switcher. Not just any switcher will do. From the datasheet. check the switcher's noise and ripple specifications, as well as its switching frequency. A typical switcher might have 10 μV rms noise over a 100-kHz bandwidth. Assuming the noise is white, this is equivalent to a noise density of 31.6 nVrms/rt-Hz over the band of interest.

Next, check the converter's power supply rejection (PSR) specification to get an understanding of where the converter's performance will degrade due to noise on the supply. 60 dB (1 mV/V) is typical for most high-speed converters over the first Nyquist zone.

Using a 16-bit ADC with 2-Vpp full-scale input range, 78-dB SNR, and 125-MSPS sampling rate, the noise floor is 11.26 n V rms. The noise from any source must be kept below this in order to prevent it from being seen by the converter. In the first Nyquist zone, fs/2, the converter noise will be 89.02 µV rms (11.26 nVrms/

rt-Hz) × sqrt(125 MHz/2). Although the switcher's noise (31.6 nv/rt-Hz) is more than twice that of the converter, remember to account for the converter's 60-dB PSRR. which will suppress the switcher's noise to 31.6 pV/rt-Hz (31.6 nV/rt-Hz  $\times$  1 mV/V). This noise is much smaller than the converter's noise floor, so the switcher's noise will not degrade the converter's performance.

Supply filtering, grounding, and layout is important too. Adding 0.1 µF capacitors to the ADC power supply pins will reduce the noise even lower than that calculated above. A simple LC filter on the power supply output may work, but a cascaded filter will suppress the switcher's noise even more. Remember that approximately 20 dB/decade is gained for each additional stage. Tightly stacked power and ground planes (≤4 mil spacing) can add inherent high-frequency decoupling to the PCB design. Lastly, good physical partitioning is key; keep sensitive analog circuits away from switching circuits. For further design assistance with power supplies and converters, contact your local ADI FAE.

> To Learn More About **How to Power Converters**

http://designnews.hotims.com/27739-101

**Contributing Writer Rob Reeder is a senior** converter applications engineer working in **Analog Devices high**speed converter group in Greensboro. NC since 1998. Rob received his MSEE and BSEE from Northern Illinois University in DeKalb, IL in 1998 and 1996 respectively. In his spare time he enjoys mixing music, art, and playing basketball with his two boys.

Have a question involving a perplexing or unusual analog problem? Submit your question to: rag@reedbusiness.com

For Analog Devices' Technical Support. Call 800-AnalogD

SPONSORED BY

# Smart power-meter-IC family offers alternative to current transformers

tility power meters often must rely on a current transformer for polyphase applications. Current transformers have drawbacks, however. They are relatively expensive and require additional copper wiring. Power thieves can also tamper with the devices using large permanent magnets. Shunt current sensors are often simpler and

less expensive, but they work only for single-phase, singleelement systems. The voltages they measure across phases are too high for the subsequent electronics and also for maintenance personnel (see "Tamper-resistant smart power meters rely on isolated sensors," EDN, March 19, 2009, pg 29, www.edn.com/article/ CA6643364).

POWER AND DATA ANALOG FRONT END TEMPERATURE SENSOR CURRENT

The 71M6541x and 71M6xx1 smart-meter ICs feature digitally isolated current sensors that Teridian based on its proprietary MicroDAA isolation technology.

The pulse transformer has enough power to eneraize the sensor IC with accuracy to ANSI 200A Class 0.2.

Teridian takes a different approach to the problem with its new SOC (system-onchip) smart-metering product family, which includes the 71M6541x and 71M6xx1. The family features digitally isolated current sensors that the company based on its proprietary MicroDAA (dataaccess-arrangement) isolation technology. The 71M6541x stand-alone meter SOC targets use in single-phase systems. For multiphase systems, designers can eliminate the need for a current transformer and its associated copper wiring by using an inexpensive pulse transformer to interface the 71M6541x to the 71M6xx1 isolated sensor IC, which then connects to a current-sensing shunt element. The 6541 sends a signal to the pulse transformer, which provides a communication signal and has enough power to energize the sensor IC with accuracy to ANSI 200A Class 0.2.

The 71M6541x comes in 64-pin LQFPs with 32- or 64kbyte flash-memory options; prices start at \$2 (10,000). The 71M6xx1 isolated sensors come in eight-pin SOIC packages for prices starting at \$1.50 (10,000), depending on current and accuracy range.

-by Margery Conner **▶Teridian**, www.teridian.com.

# CALYPTO TO POWER-MANAGEMENT EXPERTS: HAVE IT YOUR WAY

Calypto Design Systems has for some time now successfully leveraged its core technology-sequential analysis of synchronous logic circuits-into a full suite of tools to reduce power consumption. Analyzing your RTL (registertransfer-level) logic, the Calypto tools identify opportunities to apply fine-grained clock gating and fine-grained use of sleep modes in memory instances. The tools then reorganize the RTL logic if necessary, insert enable signals into the code, and provide a formal equivalence check to make sure they didn't break anything. All of this action takes place before synthesis, during which you in theory still have the most leverage over active and leakage power. The company claims that the tools can reduce power consumption by as much as 60%

This approach should be great news for teams working on power-constrained designs. Ironically, though, the one group that is in the best position to appreciate what the Calypto tools do-power-management experts-has had an issue: automation. RTL gurus don't want a tool taking liberties with their code, even if it does the right thing. Addressing that issue, Calypto recently announced the PowerAdviser flow, which the company based on Release 3.1 of its PowerPro package. In this flow, the tools analyze your RTL, and PowerAdviser makes recommendations without altering the code.

The flow offers three categories of information in its reports. First, the analyzer generates clock-gate-enable and memory-mode-enable expressions based on your RTL. You can review these expressions at your leisure and drop those that you like directly into your code. This approach is in essence a manual version of the PowerPro CG and MG tools. Second, the analyzer suggests changes to the RTL that would enable further clock- or memory-gating opportunities. For example, the tool might suggest importing a mode-control signal from upstream, making it possible to gate the clock on a register when there is no activity on the block's inputs. If you like PowerAdviser's suggestions, you can modify your RTL and then rerun PowerAdviser, which then generates the correct expressions.

Third, PowerAdviser suggests changes to your microarchitecture that would open up even more gating opportunities. For example, the tool spots registers that rarely change but are not efficiently clock-gated and registers that toggle often in situations in which their outputs don't affect other circuits. You can look into these areas of the design and, if it's appropriate, reorganize them and then return to PowerAdviser to get the enable expressions.

-by Ron Wilson

Calypto Design Systems, www.calypto.com.

# Support Across The Board.™

From Design to Delivery<sup>™</sup>

# Now, you can have it all.™

Faster and easier than ever before. Our commitment to customer service is backed by an extensive product offering combined with our supply chain and design chain services – which can swiftly be tailored to meet your exact needs. We have dedicated employees who have the experience to provide the highest level of customer service with accuracy and efficiency. All of our technical experts are factory certified on the latest technologies, providing you the expertise to move projects forward with speed and confidence.

Avnet offers the best of both worlds: extensive product and supply chain knowledge, and specialized technical skill which translates into faster time to market – and the peace of mind that comes from working with the industry's best. Avnet is ranked Best-In-Class\* for well-informed sales reps, knowledgeable application engineers and our design engineering services – proof that we consistently deliver:

- > Industry recognized product expertise

- > Specialized technical skills

Ready. Set. Go to Market.™

Visit the Avnet Design Resource Center™ at: www.em.avnet.com/drc

Accelerating Your Success™

1 800 332 8638 www.em.avnet.com

# **VOICES**

# Recognizing technology's inflections

he embedded-processor market is experiencing a lot of activity. Traditional 8- and 16-bit processor vendors are adding small 32-bit processors to their product lineups, and there is a lot of interest in small 32-bit processors, such as the Cortex M3 and M0 processors from ARM. NXP is the lead licensee for the ARM Cortex-M0 core-the most rapidly adopted core in ARM's history. Pierre-Yves Lesaicherre, senior vice president and general manager for NXP Semiconductors' microcontrollers and logic business lines, recently discussed the microcontroller market with EDN. An excerpt of that interview follows. For the full text, go to www.edn.com/100318pa.

# What is your impression of the current embedded-processor market?

The embedded market has evolved over the last 30-plus years. Suppliers with proprietary architectures have steadily built positions and niches in many evolving application segments. However, over the last few years, there has been an increasing momentum toward the adoption of the ARM architecture and the everwidening software and development ecosystem that can be harnessed to speed the development cycle and to reduce development costs. While the 8- and 16-bit markets have stopped growing or are in decline, the 32-bit market is now the fastestgrowing segment of the overall microcontroller market. As a result, most microcontroller vendors are now focusing their R&D innovation and marketing effort on new 32bit solutions, with the ARM architecture gaining increasing importance in the low

range to midrange of the 32bit market.

# How and why is the embedded-processor market changing?

Although the embedded processor was once just the processing engine, we now have differentiated application solutions and more application-centric processors that incorporate all the peripherals and resources required for a certain application or vertical segment of the market, such as e-metering, white goods, motor control, and medical. In addition, the software development and infrastructure have become major drivers and key decision factors in customer project and life cycle. Embedded developers often value a strong ecosystem and support infrastructure as importantly as the performance of the microcontroller when making their processor and vendor selection.

# What applications are most affecting or affected by

### these emerging changes?

Most industrial applications connected to energy efficiency, renewable energy, metering, motor and power control, and sensor interfacing are moving from bit-oriented control solutions-that is, 8 bits-toward math-intensive, graphical, and touch-controlled user interfaces. There is a growing need for much more interconnected control between units and nodes and within the home, building, and factory floors. With R&D budgets stagnating or even decreasing and shortening time-to-market requirements, embedded developers look for processors that better fit the needs of their applications, and they have to rely on a strong ecosystem, support, and infrastructure to speed up their development and keep innovation costs at a reasonable level.

# How do you see development tools maturing and changing?

The customer base for the embedded space is expanding. A single development environment can no longer meet the demands of this fragmented user base. For instance, NXP sees four distinct groups of users we need to serve. [First are] the traditional embedded developers. These customers are well-served by the traditional tool manufacturers, such as

Keil, IAR, and others. The customers are highly skilled in the art of writing embedded code and take great pride in building the most out of everything a microcontroller has to offer, even if it means getting down to the bits, bytes, and register-level

[The second group is] the open-source environment. This group of customers is used to the do-it-yourself method of embedded-application development. These customers are fiercely loyal to the community and have propelled the progress of IDEs such as Eclipse, operating systems such as Linux, and compilers such as GNU and LLVM.

[The third group is the engineers who need] fastprototype, proof-of-concept tools. Embedded engineers struggle to provide a streamlined way of taking an idea all the way to a demonstration to show the merit of the idea to their marketing or management team. Code size and perfecting the code are top priorities at this stage. A tool such as mbed [www.mbed. org] takes embedded programming a few levels higher: building C/C++ libraries on top of device drivers and exposing the users to a highlevel API [application-programming-interface]-driven tool that's clean and easy to

[The last group comprises] PC programmers. With the microcontroller manufacturers providing extremely capable devices with large memory and high performance at very low prices, a new group of users has entered the embedded space.-interview conducted and edited by Robert Cravotta

# "I need the fastest DMM they make."

# They don't make them any faster.

Nobody but Agilent makes a range of DMMs this fast, this accurate, or this reliable. Up to 1000 times more readings per second than the nearest competitor's, and far easier to use, you'll rip through tests in a fraction of the time. It's what you'd expect from the leader in DMM technology.

| DMM               | Digits | DC<br>Accuracy | Max<br>Readings | Function/Range<br>Changes | 10                      |

|-------------------|--------|----------------|-----------------|---------------------------|-------------------------|

| 34405A            | 5 1/2  | 0.0250%        | 19 / sec        | 0.2 sec                   | USB                     |

| 34401A            | 6 1/2  | 0.0035%        | 1,000 / sec     | .02 sec                   | GPIB, RS-232            |

| 34410A            | 6 1/2  | 0.0030%        | 10,000 / sec    | 2.6 ms                    | GPIB, USB,<br>LAN (LXI) |

| 34411A/<br>L4411A | 6 1/2  | 0.0030%        | 50,000 / sec    | 2.6 ms                    | GPIB, USB,<br>LAN (LXI) |

| 34420A            | 7 1/2  | 0.0030%        | 250 / sec       | .02 sec                   | GPIB, RS-232            |

| 3458A             | 8 1/2  | 0.0008%        | 100,000 / sec   | 3.0 ms                    | GPIB                    |

Download the latest measurement brief and tips www.agilent.com/find/fastestdmm

<sup>© 2010</sup> Agilent Technologies, Inc.

\*Prices are in USD and are subject to change.

See participating distributors for details.

# BY BONNIE BAKER

# System or technology dictates ADC choice

ow do you decide which ADC technology to use in your applications before you do a thorough system evaluation? Maybe you prefer SAR (successive-approximation-register) ADCs because you assume they are easy to use and a bit faster than delta-sigma converters. Then again, you may select delta-sigma converters because you assume they are slower but have good resolution. What the heck? Maybe you choose the ADC that you have always used.

When selecting a converter, you usually base your decision on the ENOB (effective number of bits); accuracy; repeatability, or noise; and output data rate. You may assume that SAR ADCs produce accurate outputs with medium output speeds and that deltasigma converters produce lower-noise output signals with slower output data rates. These assumptions may no longer guide you when deciding between a SAR ADC and a delta-sigma ADC.

Think about changing your design paradigm from focusing on individual devices to considering the complete system. You will find that both ADC

architectures might be appropriate for a given application. For instance, if you know the system ENOB, you may find that combining an analog gain stage with a SAR ADC matches the performance of a higher-speed deltasigma converter.

A system evaluation includes inspecting the system's sampling speeds, analyzing its accuracy, and comparing its repeatability, or noise-level, capability. To inspect sampling speeds, select a single clock frequency and allow time for the analog components to fully settle before conversion. With system accuracy, you combine the dc

> performance characteristics into a total-unadjustable-error figure of merit for comparison.

The repeatability evaluation differs from the accuracy evaluation in that it defines how consistently a value from one conversion to the next repeats itself. With a repeatability evaluation, you can combine the noise performance of the signal-chain de-

vices in terms of effective resolution.

As we examine the accuracy and repeatability in our system evaluations, we will use **Table 1** as our starting point. The circuits in the **table** encompass handheld-meter, data-logger, automotive-system, monitoring-system, and many other applications. Each system's gain ranges from one to 128. Column 2 in the **table** lists the ideal system's full-scale range referred to the input of the system. The system's LSB (least-significant bit, Column 3) is equal to the system's full-scale range divided by the number of system codes: 4096.

In my next column, I'll delve into the conversion speeds of these designs. In future columns, I'll examine the differences between a 12-bit SAR ADC, a multiplexed PGA (programmable-gain-amplifier)-SAR ADC, and a 24-bit multiplexed delta-sigma converter. The analog or digital gain range for each system will be 1 to 128V/V, and the power-supply voltage will be 5V. I'll also investigate the accuracy and repeatability of these systems.

Here is the trillion-dollar question: Which system is best for the listed applications—a PGA-SAR ADC or a delta-sigma ADC? You can reach me at ti\_bonniebaker@list.ti.com with your best guess. Be sure to include a description of your application with its basic requirements.EDN

# REFERENCES

- Baker, Bonnie C, "Analog-to-Digital Converters, Part 4 of 6: Move Your System Strategy to the Forefront in Your ADC Designs," Texas Instruments, Dec 3, 2009, www.en-genius. net/includes/files/acqt\_113009.pdf.

- **2** "Nuts and Bolts of the Delta-Sigma Converter," Texas Instruments, www.ti. com/nutsandboltsvideo-ca.

Bonnie Baker is a senior applications engineer at Texas Instruments and author of A Baker's Dozen: Real Analog Solutions for Digital Designers.

| TABLE 1 ADC COMPARISON |                                            |                             |  |  |  |  |  |

|------------------------|--------------------------------------------|-----------------------------|--|--|--|--|--|

| Analog or process gain | Full-scale range<br>(V, referred to input) | LSB (μV, referred to input) |  |  |  |  |  |

| One                    | 5                                          | 1220.7                      |  |  |  |  |  |

| Two                    | 2.5                                        | 610.35                      |  |  |  |  |  |

| Four                   | 1.25                                       | 305.18                      |  |  |  |  |  |

| Eight                  | 0.625                                      | 152.59                      |  |  |  |  |  |

| 16                     | 0.3125                                     | 76.29                       |  |  |  |  |  |

| 32                     | 0.1563                                     | 38.15                       |  |  |  |  |  |

| 64                     | 0.0781                                     | 19.07                       |  |  |  |  |  |

| 128                    | 0.0391                                     | 9.54                        |  |  |  |  |  |

# EXTREME EVOLUTION

Introducing the RX Family from Renesas.

The next-generation microcontrollers for communicating anytime, anywhere, and with anyone and anything.

- Extremely high performance: 1.65DMIPS/MHz, up to 200MHz

- Extremely small code: up to 30% smaller than previous Renesas MCUs

- Extremely low power consumption: 30µA/MHz (typical) for the core

- Extremely high integration: with up to 4MB of extremely fast embedded Flash

Stay tuned. The evolution continues.

Check the website for details.

www.america.renesas.com/ReachRX/a

Renesas Technology Corp.

+ Go to www.edn.com/pryingeyes for past Prying Eyes write-ups.

The Black and Decker GH1000 Type 2 string trimmer

fter my disappointment with the performance of string trimmers with 0.040- and 0.065-in. strings, I bought a futuristic-looking Black and Decker model that used professional-size 0.080-in. line. Around the end of the two-year warranty period, the string stopped spinning, even though the motor was still turning. Prying into the interior, I saw that the drive belt had broken and the drive pulley had melted. I replaced the belt with a \$7 belt from eReplacementparts.com. Although the company sells the aluminum drive pulley for only \$1.42, it does not offer the plastic drive pulley. I spent an hour and still couldn't figure out how to disassemble the drive pulley. I did make sure I got a spare belt; the new one won't last long.

SIP Cinderson of Suzhou, Chinanear Shanghai-makes the universal brushed motor rated at 120V and 7.2A. It has a nominal power consumption of 874W, or about 1 hp.

Inadequate structure between the motor and the drive pulley means that the cogged belt will run off the pulleys under heavy loads, such as when you are cutting thick weeds and grass.

The designers added a large flange on the driven pulley to keep the belt from flying off. They also lengthened the drive pulley to keep the belt engaged as it tries to run off the drive pulley.

Although the flange on the drive pulley prevents the belt from flying off, the side pressure creates enough friction to melt the plastic. The molten plastic solidified under the belt, eventually causing it to rip apart.

The manufacturer used several holes for fixturing during factory assembly. All the screws holding the case halves together are identical in length.

The designers covered a screw with a decal, making disassembly frustrating. Other than this problem, the design follows good Zaxis assembly practices. You can put every subassembly onto the bottom half of the case, then put on the top half and screw it together all from one direction, the Z axis.

# 您会说 MATLAB吗?

Over one million people around the world speak MATLAB.

Engineers and scientists in everything from aerospace and semiconductors to biotech, financial services, and earth and ocean sciences use it to express their ideas.

Do you speak MATLAB?

Solar Image taken by the X-Ray Telescope: supplied courtesy of Smithsonian Astrophysical Observatory.

See related article at mathworks.com/ltc

MATLAB

The language of technical computing

Image Credit: SAO, NASA, JAXA/ISAS, NAOJ ©2007 The MathWorks, Inc

# MECHATRONICS INDESIGN FRESH IDEAS ON INTEGRATING MECHANICAL SYSTEMS, ELECTRONICS, CONTROL SYSTEMS, AND SOFTWARE IN DESIGN

# Analogies give engineers insight

Insight based on fundamentals is the key to innovative multidisciplinary problem-solving.

person trying to explain a difficult concept will often say, "Well, the analogy is ...." The use of analogies in everyday life aids in understanding and makes everyone better communicators. Mechatronic systems depend on the interactions among mechanical, electrical, magnetic, fluid, thermal, and chemical elements, and most likely combinations of these. They are truly multidisciplinary, and the designers of mechatronic systems are from diverse backgrounds. Knowledge of physical system analogies can give design teams a significant competitive advantage.

Consider the exhaust system of a motorcycle and its heat shield. Temperatures have to be controlled through design for

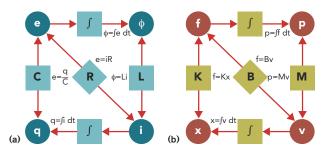

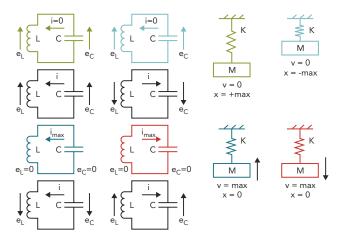

Figure 1 The model structures for electrical systems (a) and mechanical systems (b) display an obvious analogy.

Figure 2 Colored system diagrams correspond to each other.

performance but also to protect the rider. Being able to model this system as a network of thermal resistances and capacitances, just like an electrical circuit, is a powerful design tool. It allows the engineer to visualize the flow of heat and the storage of thermal energy and specify key temperatures by selection of materials and geometries that vary the network (conduction, thermal resistances convection, and radiation) and capacitances. Improving performance happens with understanding—not by trial and error—and quickly.

To explore in some depth the nature of physical system analogies, let's use the common electrical-mechanical analogy. These systems are modeled using combinations of

Kevin C Craig, PhD, is the Robert C Greenheck chair in engineering design and a professor of mechanical engineering, College of Engineering, Marquette University. For more mechatronic news, visit mechatronics zone.com.

pure (only have the characteristic for which they are named) and ideal (linear in behavior) elements: resistor (R), capacitor (C), and inductor (L) for electrical systems, and damper (B), spring (K), and mass (M) for mechanical systems. The variables of interest are voltage (e) and current (i) for electrical systems and force (f) and velocity (v) for mechanical systems. Figure 1 shows the model structures for these systems. The analogy is obvious!

We can use this analogy to explain the flow of current and the changes in voltages in an LC (inductor-capacitor) electrical circuit—difficult to envision for most mechanical engineers and even for some electrical engineers—by comparing it with a spring-mass mechanical system. Figure 2 is color-coded: Colored diagrams for each system correspond to each other. By comparing the motion of the mass—its changing potential energy corresponding to energy stored in the electric field of the capacitor and its changing kinetic energy corresponding to energy stored in the magnetic field of the inductor—one can better understand how electrical capacitors and inductors function.

For enhanced multidisciplinary engineering system design and better communication and insight among the design team members, the use of analogies is a powerful addition to an engineer's toolbox.**EDN**

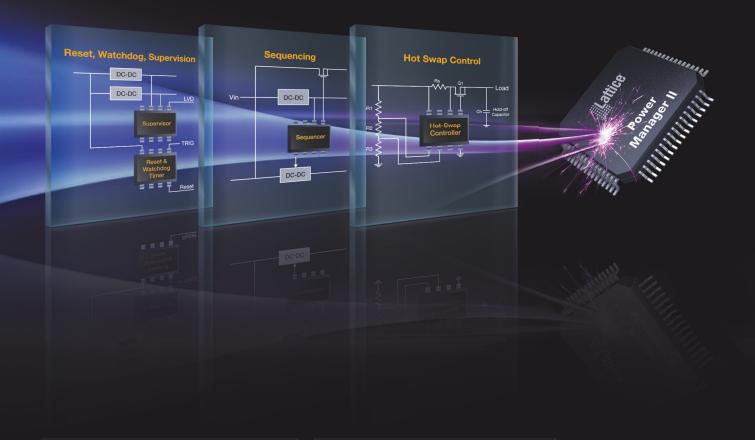

# Power Manager II. INTEGRATE POWER MANAGEMENT. LOWER COSTS.

Power Manager II features an innovative programmable core and precision analog sensors to reduce component count and increase reliability. Lattice programmability enables your power management design to meet changing requirements without major circuit redesign or a board re-spin.

Learn more about the cost-efficiencies of Power Manager solutions at:

latticesemi.com/powermanager

## **Features**

- Charge pumps for hot swap MOSFET control

- PLD for flexible supply sequencing and reset generation

- 0.2% error (typ.) programmable comparators for fault detection

- Differential sensing for centralized control

- 10-bit ADC with I<sup>2</sup>C interface for system monitoring

- High volume pricing starts at <\$1.00</li>

# And more...

# **Benefits**

- Integrate multiple functions to reduce BOM cost

- Increase fault coverage

- Reduce footprint

- Increase reliability

- Wide application coverage

- Reduce risks through programmability

# And more...

latticesemi.com/powermanager

# Peel and place thermal solution withstands the heat of solder reflow.

Thermally conductive insulated metal substrate boards specifically configured for LED applications.

Easier assembly, cooler LEDs.

Bergquist's T-Clad with pre-applied Bond-Ply®450 allows you to adhere your mounted LEDs to a variety of heatsinks and surfaces while thermally optimizing your application. This version of peel and place T-Clad can withstand the high temperatures of solder reflow during LED assembly and then be positioned in the lighting application using its strong thermally conductive adhesive.

Call or visit to qualify for your FREE sample.

FREE T-Clad® PA Sample Board

Call I.800.347.4572 or visit www.bergquistcompany.com/preapplied

18930 West 78th Street • Chanhassen, MN 55317 • A ISO9001:2000 registered facility (800) 347-4572 • Phone (952) 835-2322 • Fax (952) 835-0430 • www.bergquistcompany.com

# POLYPHASE FILTERS REDUCE SATURATION

BY RON WARNER • LATTICE SEMICONDUCTOR CORP

igital signal processing is ubiquitous in modern electronic systems, from MP3 players to digital cameras to wireless handsets. One of the mainstays of a DSP designer's tool box is the FIR (finite-impulse-response) filter. The longer the FIR filter—that is, the greater the number of taps—the better the filter's response. This situation involves a trade-off, however, because more taps require increased logic requirements, increased computational complexity, increased power consump

increased computational complexity, increased power consumption, and a greater potential for saturation or overflow.

Designers can employ polyphase techniques to implement filters that provide comparable results and use less logic, requiring fewer computational resources, consuming less power, and having less potential for saturation and overflow. The resulting filters fit into today's new class of smaller, midrange FPGAs.

### **SOME SAMPLING THEORY**

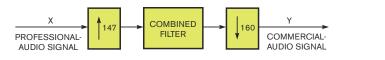

A multirate system uses multiple sampling rates. In some cases—for example, conversion of professional audio into consumer CD-quality audio—a system may sample a signal at one rate, and another portion of the system, operating

at a different rate, needs the signal. In this case, you must increase or decrease the sampling rate of the original signal as necessary. Alternatively, the data's original sample rate may be higher than an application requires. Thus, reducing the sample rate and then operating on the resulting data can dramatically decrease data-throughput requirements, reduce memory requirements, increase processing efficiency, and reduce power consumption.

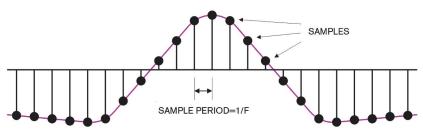

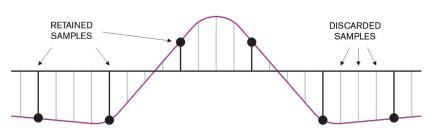

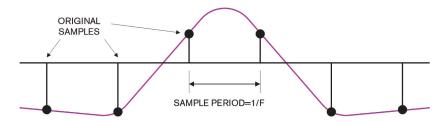

Let's first consider the problem of reducing the sample rate. Assume that your system originally sampled a signal at a frequency, F (Figure 1). Now assume that you want to reduce the sample rate to one-fourth of the original frequency. One way of achieving this reduction would be to simply throw away three of every four of the original samples (Figure 2). If you were to discard some samples, the resulting signal could contain aliasing artifacts. In the context of digital signal processing, "aliasing" refers to an effect that causes continuous signals to become indistinguishable from each other after sampling; that is, they become aliases of one another. "Aliasing" also refers to the distortion or artifacts that occur when a signal reconstructed from samples differs from the original continuous signal.

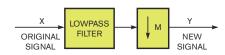

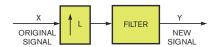

For example, consider an audio signal, such as music, that may contain inaudible high-frequency components. If you sample this signal at too low a rate, which is effectively what you are doing when you discard some samples, and then reconstruct the music with a DAC, you may hear the low-frequency aliases of the undersampled high-frequency components. To avoid this problem, you typically remove the unwanted high frequencies with a lowpass filter before discarding the unwanted samples (**Figure 3**).

Generally speaking, "downsampling" refers only to the process of discarding samples without performing the filtering operation. By comparison, "decimation" refers to the process of reducing the sample rate—that is, performing the filtering operation and then discarding the samples. In practice, the terms "downsampling," "downconversion," and "decimation" are often interchangeable. The "decimation factor," M, refers to the ratio of the input sampling rate to the output sampling rate. In this example, the input rate is four times the output rate, so M=4.

Consider a situation in which you want to increase the sample rate. The typical reason for doing so is to enable another portion of the system operating at a higher sample rate to work with the signal. Suppose that you start with a signal that the system originally sampled at frequency F (Figure 4). Now assume that you want to increase the sample

No. of addition opera-

tions per master clock

### AT A GLANCE

- In the context of digital signal processing, "aliasing" refers to an effect that causes continuous signals to become indistinguishable from each other.

- Decimation and interpolation factors can assume only integer values—that is, you can decimate or interpolate only by fractional factors.

- Digital filters are typically either FIR (finite-impulse-response) or IIR (infinite-impulse-response) types.

- FIR filters offer several advantages over IIR filters, including the fact that they have completely constant group delay throughout the frequency spectrum and they exhibit complete stability at all frequencies.

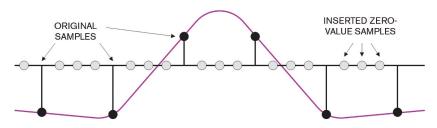

rate to four times the original frequency. You start by inserting zero-value samples between the original samples to increase the sampling rate (Figure 5). This

Three

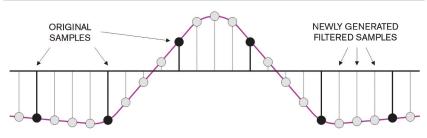

approach creates a problem, however, because the new zero-value samples add unwanted spectral components to your signal. To solve this problem, you filter the new signal to remove the undesired components and to generate more appropriate sample values (Figure 6).

Technically, "upsampling" refers only to the process of inserting the zero-value samples. By comparison, "interpolation" refers to the process of increasing the sample rate—that is, inserting the zero-value samples and then performing the filtering operation. This DSP form of interpolation differs from the classic mathematical-interpolation methods for constructing new data points from existing data points, but it's conceptually the same in that it involves generating new values from existing values. In practice, the terms "upsampling," "upconversion," and "interpolation" often are interchangeable.

"Interpolation factor," L, refers to the ratio of the output sampling rate to the input sampling rate. In this example, the output rate is four times the input rate, so L=4 (Figure 7). Note that decimation and interpolation factors can assume only integer values. That is, you can decimate or interpolate only by integer factors, not by fractional factors. In the case of decimation, for example, you can discard only an integer number of samples—that is, one of two, one of three, two of three, three of four, and so forth.

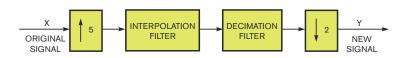

Assume that you want to modify the sample rate of a signal to interface it between two subsystems. If the ratio of the sample rates of the subsystems is an integer value, then you need only perform decimation or interpolation. However, if the ratio of the sample rates is a fractional value, then you must perform resampling, a combination of decimation and interpolation. For example, to resample by a factor of 2.5, you would first interpolate by a factor of five and then decimate by a factor of two to produce an output with a sampling rate of 5/2=2.5 that of the input sampling rate

Figure 3 You must filter the signal before discarding any samples.

#### FABLE 1 SAMPLE DECIMATION IMPLEMENTATIONS Conventional Polyfilter 1 with four Polyfilter 2 with one eight-tap FIR filter two-tap subfilter two-tap subfilters No. of multipliers Eight Eight Two No. of adders Eight Nine Three No. of multiplying Eight Two Two operations per master clock

Three

Figure 1 The original signal has a sample rate of F Hz.

Eight

Figure 2 The new signal has a sample rate of F/4 Hz.

Figure 4 The original signal has a sample rate of F Hz.

Figure 5 You can augment the original signal with zero-value samples.

Figure 6 The final signal has a sample rate of 4×F Hz.

Figure 8 In the resampling, the interpolation factor, L, is five and the decimation factor, M, is two.

Figure 9 In a resampling of professional to commercial audio, L=147 and M=160.

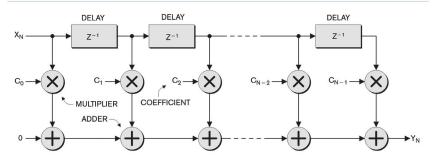

Figure 10 In a generic FIR filter, the input samples,  $X_{N}$ , pass through a series of buffer registers,  $Z^{-1}$ , corresponding to the Z-transform representation of a delay element.

Figure 7 You filter the signal after inserting zero-value samples.

(Figure 8). In practice, this approach combines the interpolation and decimation filters in Figure 8. The term "resampling factor" refers to the ratio between the output sampling rate and the input sampling rate. Regardless of the frequencies involved, you can express this figure as the ratio between the interpolation and decimation factors, L/M, which is 5/2=2.5 in this case.

As another example, consider the process of resampling a professional audio signal captured at a sample rate of 48 kHz for use in consumer audio equipment requiring a sample rate of 44.1 kHz. In this case, the resampling factor equals the ratio of the output rate to the input rate: 44.1 kHz/48 kHz=0.91875 kHz. Looking at this another way, you must change the sampling rate from 48,000 Hz to 44,100 Hz, which means that the output-toinput ratio is 44,100/48,000=441/480= 147/160 kHz. Because 147 and 160 have no common factors, you must stop at this point, which means that you must interpolate by a factor of 147 and then decimate by a factor of 160 (Figure 9).

Once again, you can express the resampling factor as the ratio between the interpolation and the decimation factors, L/M, which is 147/160=0.91875. Not surprisingly, this value is exactly the same as the one you obtained from the ratio of the output and input sampling rates because you derived the required interpolation and decimation factors from these rates.

# **INTRODUCING FIR FILTERS**

Digital filters are typically either FIR or IIR (infinite-impulse-response) types. IIR filters use feedback and tend to mimic the response of traditional analog filters. The use of feedback means that their impulse response is recursive and extends over an infinite period of time. Although they require fewer computations than FIR filters, IIR filters may have stability issues, and they cannot match the performance of FIR

Figure 11 In a symbolic representation of a decimation subsystem using a conventional eight-tap FIR filter, assume a decimation factor of four and assume that the master clock is running at some frequency.

Figure 12 In a polyphase implementation, you could split your original eight-tap FIR filter into four two-tap subfilters.

filters. In comparison, a FIR filter has no feedback, which means that its impulse response lasts for a finite duration of time. FIR filters offer several advantages over IIR filters, including the fact that they have completely constant group delay throughout the frequency spectrum and they exhibit complete stability

at all frequencies, regardless of the size of the filter.

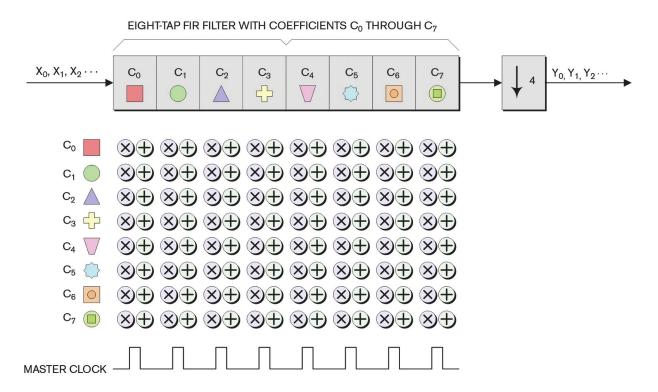

In a generic FIR filter, the input samples,  $X_N$ , pass through a series of buffer registers,  $Z^{-1}$ , corresponding to the Z-transform representation of a delay element (**Figure 10**). The filter works by multiplying an array of the most recent

N data samples by an array of constants, or tap coefficients, and summing the elements of the resulting array. By varying the weights, or values, of the coefficients and the number of filter taps, a FIR filter can realize virtually any desired frequency-response characteristic. The problem is that a FIR filter may require hundreds of taps to achieve its desired goal. Each tap requires a MAC (multiply/accumulate) unit, which consumes logic resources. Also, each tap performs a multiplication operation and an addition operation on every clock, which consumes power.

## PERFORMING DECIMATION

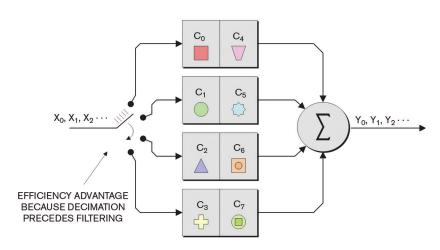

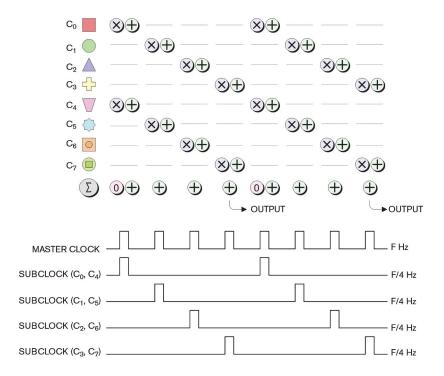

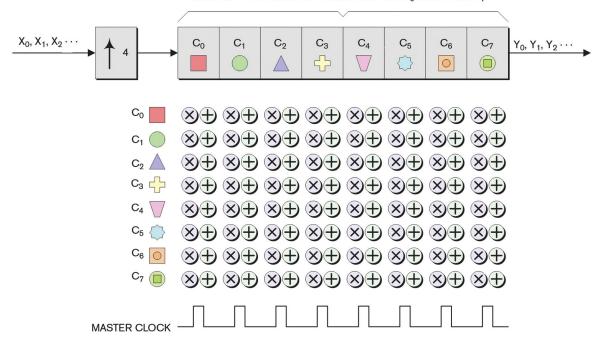

The underlying concept of polyphase filters is to split a FIR filter into a number of smaller elements and to then combine the results from these elements. First, consider a symbolic representation of a decimation subsystem using a conventional eight-tap FIR filter (Figure 11). Assume a decimation factor of four and assume that the master clock is running at some frequency, F. As usual, you discard any unwanted samples after the filtering operation has taken place,

Figure 13 Each of the four subfilters is effectively running at a frequency of F/4 Hz.

Figure 14 You use each of the four subfilters in this initial polyphase implementation only one-fourth of the time, so you require only one of them at any time, which leads to a slightly more refined implementation.

| TABLE 2 SAMPLE INTERPOLATION IMPLEMENTATIONS   |                                   |                                           |                                         |  |  |  |  |

|------------------------------------------------|-----------------------------------|-------------------------------------------|-----------------------------------------|--|--|--|--|

|                                                | Conventional eight-tap FIR filter | Polyfilter 1 with four two-tap subfilters | Polyfilter 2 with one two-tap subfilter |  |  |  |  |

| No. of multipliers                             | Eight                             | Eight                                     | Two                                     |  |  |  |  |

| No. of adders                                  | Eight                             | Eight                                     | Two                                     |  |  |  |  |

| No. of multiplying operations per master clock | Eight                             | Two                                       | Two                                     |  |  |  |  |

| No. of addition operations per master clock    | Eight                             | Two                                       | Two                                     |  |  |  |  |

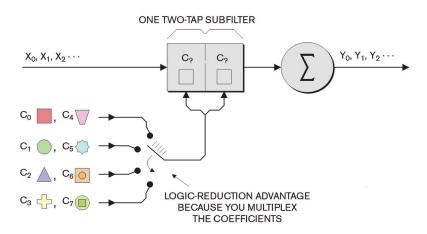

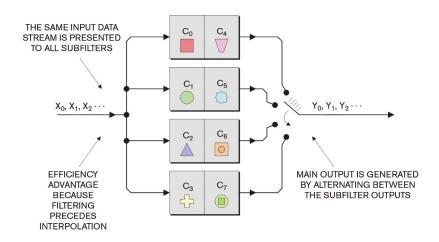

but this approach is inefficient because it means that you are performing the filtering at the full clock frequency. In other words, every tap stage performs a multiplication and an addition on every clock. In comparison, in a polyphase implementation, you could split your original eight-tap FIR filter into four two-tap subfilters (Figure 12).

Assuming that the same master clock runs at some frequency, F, you can visualize the input data stream as feeding into a rotating switch, which you would implement using standard logic techniques. You feed the first data value to the first subfilter, the second data value to the second subfilter, the third data value to the third subfilter, and the fourth data value to the fourth subfilter. You then loop around so that you feed the fifth data value to the first subfilter, the sixth data value to the second subfilter, and so on.

Using subfilters reduces the potential for saturation and overflow. You typically handle any saturation or overflow that might occur only in the final summing function. In addition, using subfilters provides an immediate efficiency advantage because you are effectively decimating the data before performing the filtering operation. It also means that each of the four subfilters is effectively running at a frequency of F/4 Hz (Figure 13).